今年6月,英特尔宣布收购一家名为“Barefoot”的公司,旨在帮助英特尔的数据中心部门“更好的应对云数据中心客户的不断变化的各类需求”。伴随着收购,Barefoot的CEO兼总裁,Craig Barratt博士(下图右)被任命为英特尔数据中心部门旗下“互联事业部(connectivity group)”的总经理,负责英特尔以太网控制器、网卡、交换芯片等一系列网络互联产品。

很多读者也许并没有听说过Barefoot这个公司。事实上,它的飞速发展已经对诸如博通和英特尔等传统网络交换芯片厂商形成了逼宫之势,大有一种“光脚的不怕穿鞋的”之感。

在这篇文章中,老石将详细解读这家“赤脚”公司的四大核心竞争科技:

- 一种编程语言:P4

- 一种可编程芯片架构:PISA

- 一种编译器与工具链:P4 Studio

- 一种可编程网络芯片:Tofino

文章最后,老石将分析Barefoot的这些“黑科技”对FPGA在网络应用的影响。

一种编程语言:P4

早在2014年,Barefoot与英特尔、谷歌、微软,以及斯坦福大学和普林斯顿大学联合发表了一篇名为《P4:Programming Protocol-Independent Packet Processors》的论文,这也代表着P4编程语言的正式诞生。

P4本质上是一门针对网络数据包处理的领域专用语言(Domain Specific Language)。从它的全称可以看出,P4最主要的特点就是与具体的网络协议无关,这与当前正在蓬勃兴起的SDN(软件定义网络)概念不谋而合。

在一个SDN网络中,通常可以将其划分成控制平面和数据平面两部分,这也是它有别于普通网络的最本质特点。其中,控制平面负责对数据平面的各种网络设备进行集中管理和配置,二者通过标准化的接口进行互联。控制平面往往基于标准CPU实现,因此有着很强的可编程性。而数据平面的传统实现,则是基于各家网络设备厂商、针对不同网络功能提供的各种设备。这样的实现方式,说好听一点是“百花齐放”,说现实一点就是“杂乱无章”、“各自为战”。由于各种设备和网络协议之间的兼容性和通用性不足,极大的限制了SDN数据平面在规模和功能上的扩展能力。

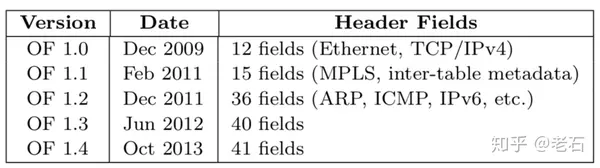

在现有的SDN网络中,控制和数据两个平面之间的标准化接口通常使用OpenFlow,很多网络设备供应商也相继推出了很多支持OpenFlow编程的网络硬件。然而,OpenFlow标准与网络协议紧密相关,它的多次版本更迭都是为了增加对更多协议的支持,见下图。

随着网络流量的爆炸性增长,各种新的网络协议层出不穷,比如在云数据中心里,各类隧道和封装协议(如VXLAN等)已经被普遍采用。除此之外,很多网络设计者也希望使用自定义或非公开的网络协议,以更好的满足自己和客户的定制化需求。这些新型的应用场景,一方面需要OpenFlow不断更新标准,另一方面需要硬件厂商不断更新硬件,以支持这些新兴协议。而这不管从成本还是时间上看,显然不能满足网络的发展需要。

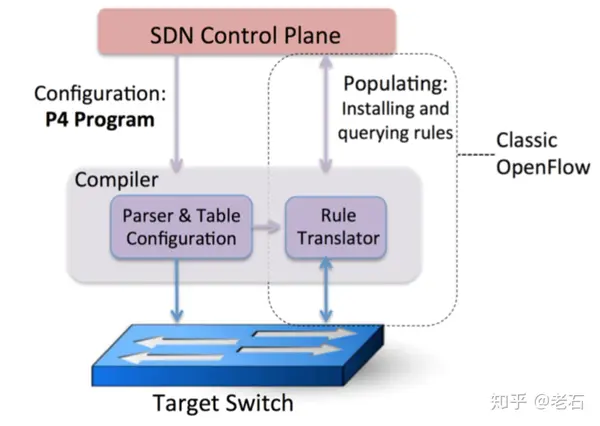

事实上,P4诞生的最主要目的就是为SDN的数据平面提供协议无关的可编程能力。如下图所示,网络设计者可以通过P4定义数据平面的转发和处理规则,例如报头解析、匹配、表项配置等,然后通过编译器在目标交换机上进行实现。

P4作为一个开源的领域专用语言,发展至今天已有相当的规模,拥有包括英特尔、赛灵思、微软、谷歌、思科、阿里、腾讯等几十家科技公司和大学的代码贡献和支持。

有关P4语言的具体技术细节,本文不再展开,有兴趣的读者请在公众号后台回复关键字“P4”,或进入知识星球“老石谈芯-进阶版”查看技术资料并参与讨论。

值得注意的是,OpenFlow和P4均出自一个大师的手笔,那就是斯坦福大学教授Nick McKeown。作为SDN的提出者和先驱,他先后发起成立了开放网络基金会(ONF),以及负责制定P4标准的http://P4.org。此外,他也是多个初创企业的创始人,其中就包括这篇文章中介绍的Barefoot:McKeown教授在Barefoot公司担任联合创始人和首席科学家。

业界有“一流的企业做标准”的说法。Barefoot公司作为P4语言的主要发起者,又由SDN领域最有权威的大牛创办,因此在业界的影响力不言而喻。

一种可编程芯片架构:PISA

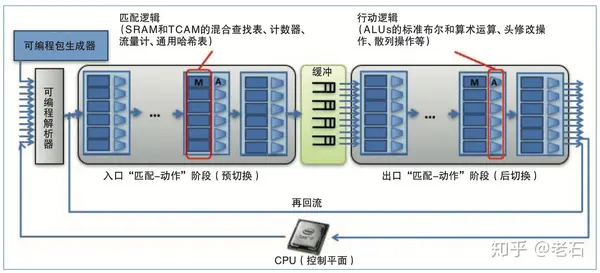

Barefoot的核心竞争力之一,就是提出了一种通用的、协议无关的、可编程的交换机芯片架构:PISA(Protocol Independent Switch Architecture)。

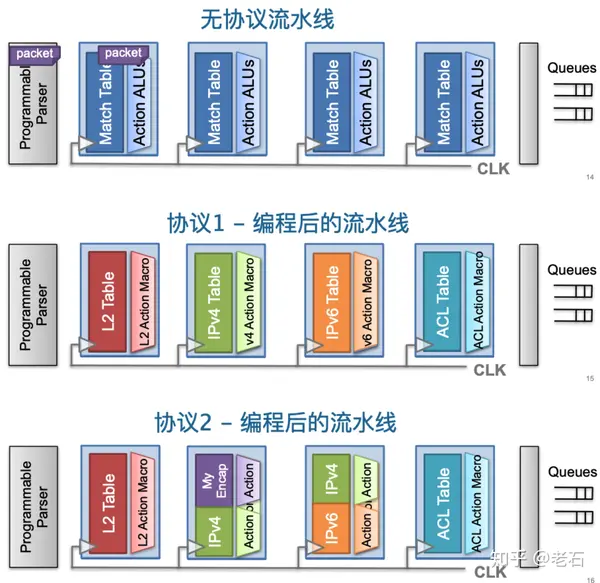

PISA的架构示意图如下所示。它的主要数据通路是由大量“匹配-动作”单元以流水线的方式组合而成。在流水线入口,有一个可编程的包头解析器,负责对数据包进行预处理和解析。此外,流水线还有一条回流路径,适用于数据包需要进行多次解析和反馈处理的情况。

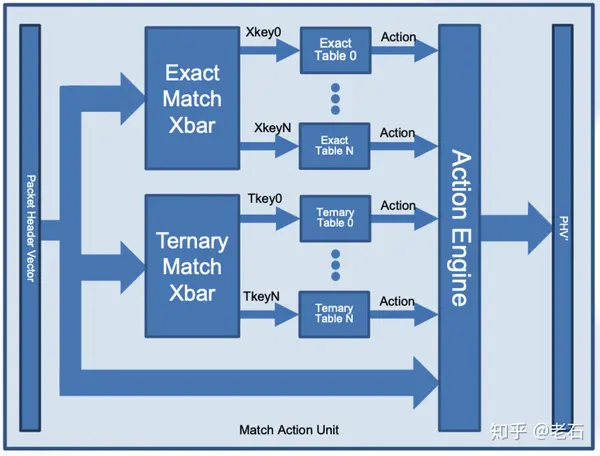

对于每个“匹配-动作”单元,它的微架构如下图所示。可以看到,它里包含多个并行的由SRAM和TCAM组成的查找表单元,可以同时进行大量的精确匹配和三元匹配。查找后的表项再通过ALU进行计算和修改,组合成新的包头传递到下一级流水线。

PISA这种架构由通用的逻辑单元和流水线组成,因此与具体协议无关,并且可以通过编程实现各种标准或自定义的网络包处理规则,而无需进行架构修改,如下图。

一种编译器和工具链:P4 Studio

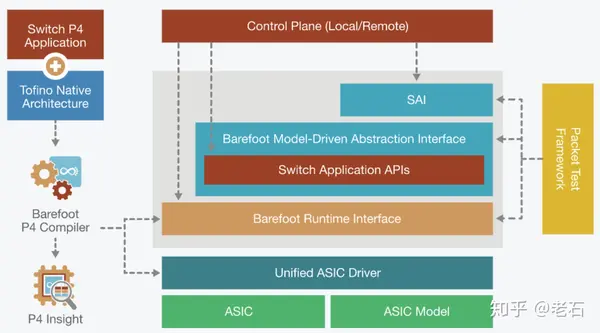

有了编程语言P4和底层架构PISA,自然需要编译器将二者进行映射。为此,Barefoot有着名为P4 Studio的编译器和开发套件。它的功能就是将P4语言描述的数据包处理规则,完整、正确的映射到PISA架构上。其功能架构如下图所示。

P4 Studio主要包含以下几个主要部件:

- P4编译器、调试器和IDE。

- P4语言的仿真环境和测试框架。

- 底层硬件的通用接口和驱动。

- 对开源网络操作系统的支持,如HPE的OpenSwitch、微软Azuere的SONiC和Facebook的FBOSS等。

有了全新的编程语言、编译器和系统架构,一款全新的可编程网络芯片就诞生了。

一种可编程网络芯片:Tofino

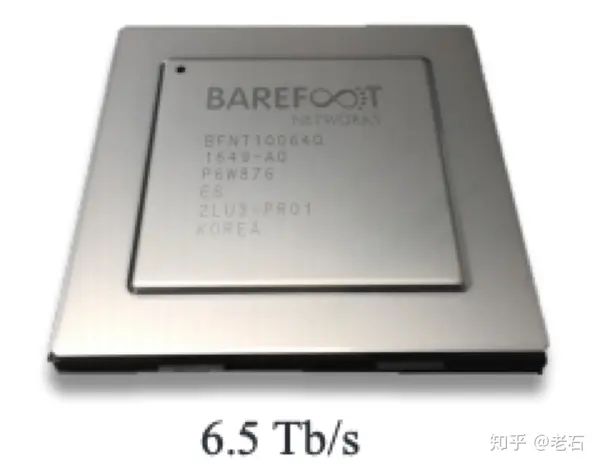

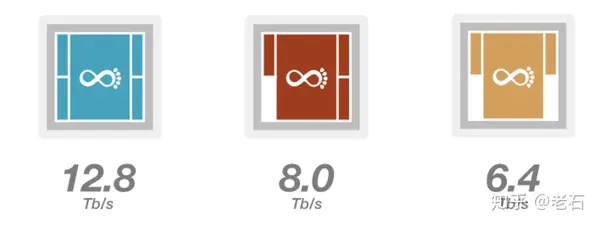

Tofino是Barefoot推出的首款可编程交换芯片,它基于台积电16nm FinFET+工艺制造。在推出之时,Barefoot称这款芯片是世界上最快的交换芯片,性能可以达到6.5Tb/s,与博通等公司的旗舰产品性能不相上下。同时,Tofino基于PISA架构,能通过P4语言进行现场编程,又有着ASIC基本的功耗和成本数据,这也是它有别于其他“传统”网络交换芯片的最大特点和优势。

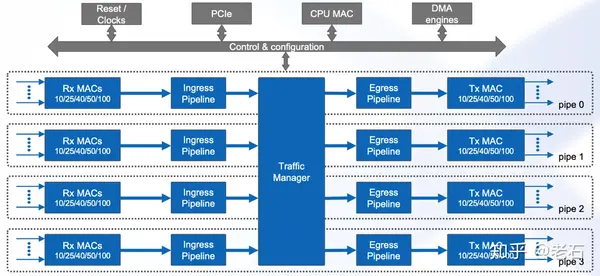

Tofino的芯片架构示意图如下所示。可以看到,Tofino有着4条PISA架构的流水线,并通过同一个TM负责四条流水线之间的流量调度和管理,最多可以支持130万条IPv4路由。在每条流水线里,包含16个100G MAC,也可以配置成10G/25G/40G/50G等多种模式

目前,Barefoot又推出了第二代Tofino芯片,它基于7纳米工艺制造,性能提升了一倍,最高支持12.8Tb/s的数据包处理速率。

基于P4的可编程网络芯片对FPGA的影响

网络数据处理和加速一直是FPGA最主要的应用领域,在之前文章中曾介绍过,英特尔近期刚刚进行了组织架构调整,将FPGA和网络平台部门合二为一,足可见对FPGA在网络领域的重视。在SDN和NFV的应用中,也有很多实用FPGA进行网络功能卸载和加速的案例,在老石之前的文章中也详细介绍过的智能网卡等等。

不过,FPGA的开发难度一直是制约其广泛使用的最大障碍之一。因此,使用诸如OpenCL等高层次语言对FPGA进行编程开发就成了业界和学术界研究的热点之一。

近年来,这类研究的重点开始转向对领域专用语言的探索,正如网络领域的P4语言。前文提到,英特尔和赛灵思都是http://P4.org的成员和代码贡献者之一,两家公司都在进行使用P4语言编程FPGA的相关研究。

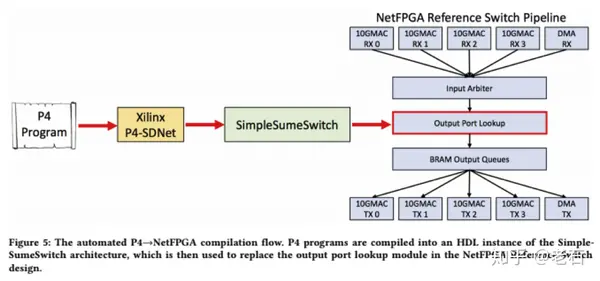

在2019年的FPGA大会上,赛灵思和Nick McKeown教授以及剑桥大学联合发表了一篇讨论P4编程FPGA的论文,它使用了赛灵思的P4-SDNet编译器生成底层Verilog代码模块,然后映射到名为“NetFPGA”的参考设计上,见下图。

这篇论文及其他FPGA’19大会的重要论文,老石在之前的文章中进行过详细梳理,有兴趣的读者可以在公众号“老石谈芯”后台回复“FPGA19”查看论文全文。

对于英特尔,在收购Barefoot之前,它就也已经开始了P4编程FPGA的研究,在最近发表的一篇白皮书中(下图),英特尔和Netcope公司合作开发了一款使用P4编程FPGA智能网卡,并得到100G吞吐量的应用实例。此外,P4语言的最初作者之一Dan Daly,一直在英特尔担任主任工程师。在收购Barefoot之后,相信对无论是FPGA还是ASIC在内的各种英特尔芯片采用P4编程会是极大的促进。

结语

Barefoot作为一个“出身名门”的初创公司,很好的把握了现在网络体系架构发展的最大痛点,提出了已经成为业界标准的P4语言,开发了对应的PISA芯片架构和编译器,并做出了两款可以完全编程的高性能网络交换芯片,可以说构建了完整的技术闭环。如今被英特尔收购,对双方都有极大的好处。Barefoot的整个创业过程和理念,值得各家芯片创业公司借鉴。

本文提到的全部技术资料、论文和演示文档等,欢迎在公众号“老石谈芯”后台回复关键字“P4”,或进入知识星球“老石谈芯-进阶版”进一步查看。

最后推荐几本FPGA开发、AI算法和程序设计相关的专业书籍,供大家参考。

注:本文仅代表作者个人观点,与任职单位无关。

本文系老石原创,如需转载请先联系老石获取授权。

关注公众号“老石谈芯”,看更多原创芯文、芯情、芯事

*更多芯片与FPGA技术解读,欢迎加入知识星球:“老石谈芯-进阶版”,一个关乎技术与观点的互动社区*

编辑于 2020-02-24 · 著作权归作者所有